1) 웨이퍼의 종류와 특성을 해석하고 설명

2) 고체의 에너지 밴드갭 분류에 의한 도체,부도체, 반도체

3)불순물을 포함하지 않은 진성 반도체와 불순물을 포함한 불순물 반도체

반도체 란?

1)물질의 종류

부도체 : 에너지갭이 커서 전자가 전도띠로 쉽게 이동할 수 없는 물질 > 4eV

도체 : 전도띠와 가전자띠가 서로 겹쳐있어서 전자가 쉽게 이동할 수 있는 물질 0

반도체 : 에너지갭이 작아서 조그마한 힘을도 전자가 전도띠로 쉽게 이동할 수 있는 물질 0~4 eV

eV : 일렉트론볼트

원자에서 전자를 하나 떼어낼 때 필요한 에너지

>전자 하나가 1 볼트의 전위를 거슬러 올라갈 때 드는 일

2) 반도체의 종류

진성 반도체

:불순물이 포함되지 않는 순수한 반도체 Ge,SI, C 등의 4족 원소

외부에서 전압을 가해도 전기가 흐르지 않는다. 안정된상태이기 때문에(공유결합)

전자와 정공의 쌍생성과 재결합 > 자유전자와 정공을 동시에 발생(EHP)

자유전자와 정공이 생겨도 진성 반도체는 시간이 지나면 서로 결합하면 소멸

EHP의 수명시간이 길 경우 소수 캐리어의 생존시간을 높일 수 있습니다.

캐리어밀도가 매우 낮음. -> 반도체로 사용 불가 > 불순물을 첨가하여 캐리어 밀도를 높임

캐리어 이동도

: 전기장내애서 반도체의 캐리어가 얼마나 빨리 이동하는지

진성 반도체의 불순물의 농도가 낮아서 캐리어 이동도는 매우 빠름 하지만 밀도가 매우 낮기 때문에 별로

하지만 이러한 특성을 이용해서 탄소구조에 의한 이차원 전자가스(2DEG)를 이용한 반도체소자(HEMT)를 만들기도 한다.

페르미준위

가전자대와 전도대 사이에 전자가 있을 확률이 50%인 에너지 준위

진성 반도체는 띠간격의 중앙에 페르미준위가 위치

실리콘의 순도

실리콘의 결정은 전기 전도도를 고려해야 함으로 순도가 매우 높아야 한다. 순도는 최종 제품의 성능을 결정하는 핵심 역할

보통 11N의 실리콘 잉곳을 사용

불순물반도체

불순물을 혼합하여 캐리어밀도를 높인 반도체

: N형반도체 - 5가의 불순물을 포함한 반도체 -> 케리어가 전자 (P,As,Sb)

P형반도체 - 3가의 불순물을 포함한 반도체 > 다수 케리어 정공(B,Al,Ga,In)

n형

페르미 준위가 전도대 쪽으로 치우져짐

불순물을 도너, 그 준위를 도너 준위라고 함

P형

페르미 준위가 가전도대 쪽으로 치우져짐

불순물을 억셉터, 그 준위를 엑셉터 준위라고 함

1.반도체의 역할

1)정류 작용

전기신호는 직류(DC)와 교류(AC)

교류를 직류로 바꾸는 작업을 정류고 이를 하는 반도체를 다이오드

한쪽 방향으로만 전류가 흐르도록 한다.

2)증폭작용

약해지는 전기신호를 정상적으로 전달하기 위해서 원상태보다 크게하는 작업

이를 하는 반도체가 트렌지스터

베이스에 작은 신호를 입력하게 되면 컬렉터에서 큰소리 증폭되서 나온다.

3)변환작용

진기신호를 빛으로 빛을 전기신호로 바꾸어줌

LED 반도체 : 전기를 빛으로 바꿔주는 반도체

CCD, CIS 반도체 : 빛을 전기신호 바꿔주는 반도체

4)전환 작용

연속적인 아날로그 신호를 불연속적인 디지털로 때로는 반대로 변환하는 작용

A/D변환(아 >디), D/A변환기(D>A)

5)저장, 기억

메모리 반도체 - 데이터를 기억, 저장

SSD : HDD보다 읽기 및 쓰기가 빠르다, 기억 밀도가 높다, 소비전력이 적다, 진동에 강하다

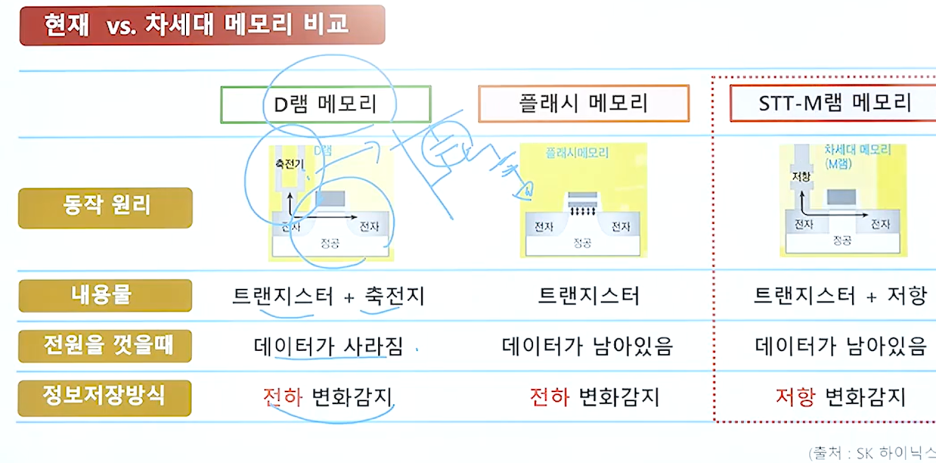

휘발성 메모리 : 전원차단시 데이터 지워짐 > D램

비휘발성 메모리 : 데이터 안 지워짐 > 롬, 플레시메모리

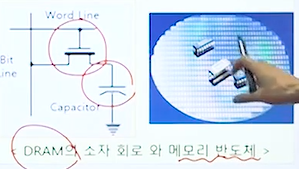

케패시터에 데이터 저장

6) 논리, 연산, 제어

논리 소자 : 전자계산기 처럼 수치 정보를 계산하는데 사용

마이크로프로세서 : CPU를 단일 IC칩으로 만든 반도체 > MPU > PC에 많이 사용

마이크로컨트롤러 : CPU+메모리 + 하드웨어제어 회로 > MCU > 특별한 목적의 기기 제어용으로 사용

2. 반도체 집적회로(IC)

1)반도체 소자란?

다이오드, 트렌지스터 소자를 직접한 소자

다이오드 : 정류작용

P형과 N형의 접합 , 전파에서 소리를 끄집어 내는 검파작용

트렌지스터 : 증폭작용 및 스위치(on/off)역할

PNP / NPN방식

직접회로

트렌지스터나 다이오드 같은 개별소자들을 모아둔 회로 > 제품의 소형화

트렌지스터 - 전원 on/off하는 스위치 역할

캐패시터 - 전하를 충전 보관하는 창고

저항 - 전류의 흐름을 조절

다이오드 - 신호를 고르게 전하는 역할

2)IC의 제조

회로설계 > 포토 마스크 제작 > 포토공정(웨이퍼위에 PR에 인화)

회로설계

CAD를 이용하여 회로를 설계(레이아아웃)

포토마스크(레티클) 제작

석영으로 만든 포토마스크위에 크롬으로 미세회로를 형상하여 포토마스크(래티클)을 제작

마스크는 보다 세밀한 패터닝을 위해 반도체 회로보다 크게 제작되고 렌즈를 이용하여 빛을 축소해 조사

3. value chain

설계(펩리스) / 생산(파운드리) / 패키징 및 테스트

1)반도체 분류 : 메모리, 비메모리반도체

메모리 : 램,롬, 플레시 > 소품종 대량생산

비메모리 : 정보처리 > 다품종 소량생산

1. 메모리 반도체

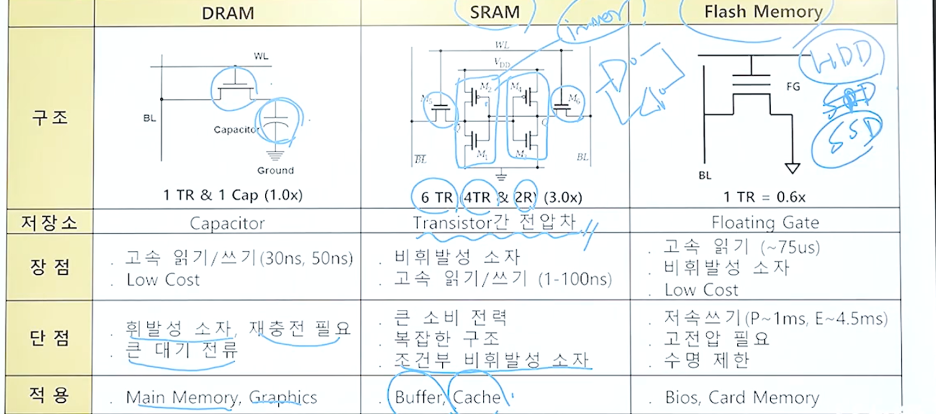

1)램과 롬

램 : 휘발성, D램

롬 : 비휘발성, 플레시메모리

D램 : 1Tr + 1 Cap, 용량이 크지만 속도가 느리고 싸다, PC의 메인 메모리

S램 : 6개의 Tr, 속도가 빠르지만 비쌈, PC의 캐쉬메모리

2)롬

PROM : 1번 다시 쓰기 가능

EPROM : 무한대로 다시쓰기 가능

EEPROM : 무한대로 다시쓰기 가능

FLASH : 데이터를 지우고 다시 기록할 수 있는 비휘발성 메모리 > 디카, 스마트폰, USB, SSD

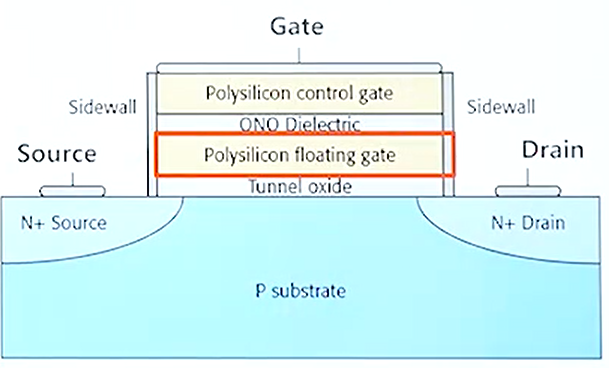

3)Flash메모리의 구조

기본 MOSFET구조에서 게이트와 채널상에 Tunneling Oxide와 Floating Gate 또는 Charge trap이 추가된 구조

사진 설명을 입력하세요.

Floating gate에 데이터 저장 > 위아래로 절연체로 둘러싸여있기 때문에 데이터 손실X

1세대 : 도체인 floating gate에 전자저장

2세대 : 절연체인 nitride를 charge trap으로 사용하여 정보 저장

mosfet구조(n형)

Metal + Oxide(절연막) : gate / Source / Drain / P 기판

4) NAND/NOR FLASH

NAND :

직렬구조 및 블록 단위로 동작

읽기는 느리지만 쓰고 지우는 것이 매우 빠름

/ 셀 면적 및 제조 단가가 저렴(고밀도)

NOR :

병렬구조 및 셀 단위 동작

쓰기 매우 느려 대용량 저장 단점

셀 면적이커서 단가가 비싸고 저밀도

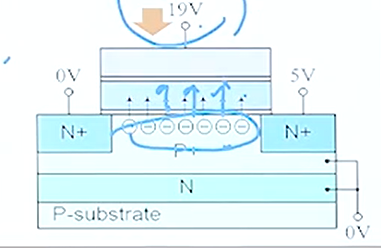

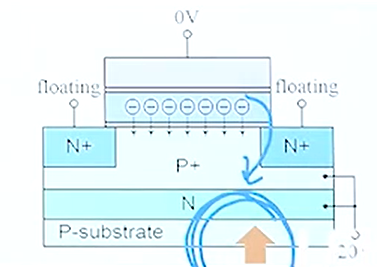

5)플레시 메모리에 동작 원리

쓰기

gate에 고저압인가 > channel에 전하가 Tunneling을 뚫고 Floating gate로 이동하여(터널효과) 충전

플로팅 게이터에 전하가 있으면 0>기판에 전하가 거의 없어서 Vth높음

지우기

기판에 고전압 인가 >gate 축적된 전하가 다시 channel로 이동하여(터널효과) 방전

플로팅게이트에 전하가 없으면 1로 인식>기판에 전하가 많아서(채널이 쉽게 형성) , Vth작다.

> 읽고 쓰기 반복하면 산화막이 손상되어 수명이 짧아지는 단점

Vth : 문턱전압

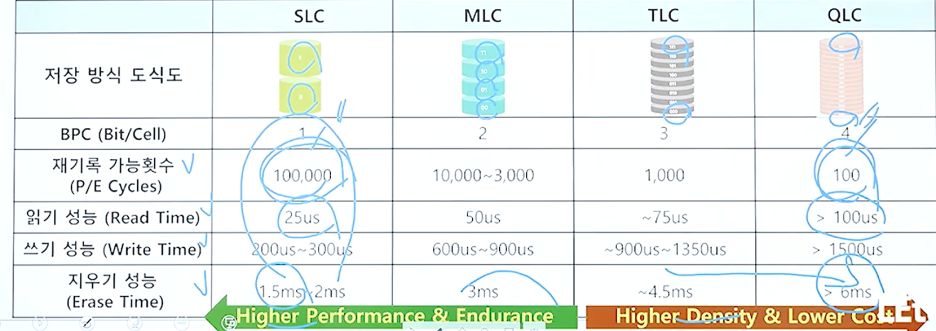

6) 플레시 메모리의 종류

사진 설명을 입력하세요.

SLC : 하나에 셀에 1bit > 작업이 단순하여 오류가 적고 속도가 빠르다. > 자동차, 항공기 등 고성능 고사양에 사용

MLC : 하나에 셀이 2bit, TLC : 하나에 셀에 3bit, QLC : 하나의 셀에 4bit

>더 작은 공간에 많은 데이터 저장 가능 한 웨이퍼당에 Net die 수가 증가해 원가 경쟁력이 높다. > 데이터센터, 서버, USB, PC등 다양한 분야에서 사용

7) 2D vs 3D NADN Flash

2D NAND

수평구조, 집적도가 증가함에 따라 패턴간의 거리가 가까워져 간섭현상이 심해짐 > 10나노가 한계

선폭이 미세해져 공정의 문제점 발생 > floating gate 전하 밀도 감소, gate to gate 커플링

3D NAND

수직으로 쌓는 구조, 3차원 수직 구조

층마다 높이에 여유를 둬 간섭현상 방지, 한정된 공간에 미세화 고용량 구현

8) 차세대 메모리

DRAM과 NAND플레시의 미세화와 집적화 한계를 극복이 목표

>oxide에 터널 현상을 이용해서 정보를 저장하므로 수명이 줄어드는 단점이 있음.

주기어장치(RAM)

보조기어장치(NAND flash)

MRAM

: 전자의 스핀 방향에 따라 0,1저장

ReRAM

: 필라멘트현상을 이용, 부도체의 저항 변화에 의한 전류흐름 유무를 ㅣ용

P램

: 결정과 비 결정의 상변화로 0,1저장

칼코게나이드 글라스 사용

2.시스템 반도체

논리, 연산, 제어 기능을 수행하는 반도체

1) 종류

마이크로컴퍼넌트(MPU,MCU,DSP)

아날로그 IC

로직 IC

DDI - RGB화소의 트랜지스터를 조정

광학반도체 - CIS, CCD

AP

개별소자

2) 무어의 법칙

칩의 집적도는 18개월마다 2배씩 증가

3)인텔의 틱톡전략 : 무어의 법칙을 토대로 한 intel의 신제품 출시 전력

틱: 기존의 설계를 바탕으로 미세 공정을 개선해 선능을 높이고

톡: 완전히 새로운 설계를 기반으로 칩을 개발

+최적화 단계를 새로 넣은 모델 : 최근 난이도 증가로 사실상 사이클의 기간이 2~3년으로 증가하면서 무어의 법칙의 1년 6개월마다 집적도 2배 증가는 변화 예상

-> 포토 공정의 난이도가 증가하고 있는 때문에

> EUV(극자외선)기술 필요 > 제한된 웨이퍼 공간에 더 많이 집적하고 선능과 전력효율을 향상시키기 위해

4)EUV 장비 성능 및 이슈

광원 : 기존 ArF 포토방식은 관원으로 엑시머 레이저를 사용했으니 EUV레이저는 플라즈마를 사용. > EUV는 액체금속인 주석을 노즐로 떨어 뜨리면서 플라즈마를 발생시키는 방식으로 광원을 형성

광학 방식 : 기존 방식은 렌즈를 사용하는 반면 EUV는 주로 거울을 사용

EUV의 광원의 파장은 13.5nm

이슈 및 과제 : EUV는 이론상 싱글 패터닝 기술로 멀티 패터닝에 비해서 제조시간을 단축시켰다.

하지만 제조 공정상 Metal Contamination 이슈 및 출력이 250이상을 축력이 나와야 한다.

> 처리량(wph) : 시간당 200매 이상 웨이퍼를 처리해야한다.(현자 ArF는 기간당 275 WF처리)

1. 시스템 반도체

1)모바일 AP

CPU, GPU(그래픽), MMP(비디오압축해제), DSP(오디오신호처리) 등의 시스템 장치, 인터페이스를 하나의 칩에 집적한 것은 SoC : System -on -Chip)이라고 함

모바일 기기에 특화된 모바일 D램과 모바일 AP를 하나의 패키징 적층한 것을 POP:Package on Package라고 함

2) 저장장치

- 낸드플래쉬 메모리와 컨트롤러가 패키지로 통합된 eMMC(병렬방식)

- 모바일D램과 함께 하나의 패키지에 적층 (eMCP)

- 최근 솔루션 : eMMC 스토리지와 SD카드

UFS : 모바일 저전력용 embedded SSD > 특징 : LVDS 직렬 인터페이스로 동시에 읽고 쓰는 상방향 소통

3) 퀄컴 스냅드래곤 835 특징

- 삼성전자 10nm FinFET 공정

- 기존 ArF방식을 이용하여 트리플패터닝 기술을 적용 > 미세공정 한계 극복

4) 삼성전자의 엑시노트9

8개의 코어와 AI기능을 특화한 NPU추가로 탑재

5) FinFET공정

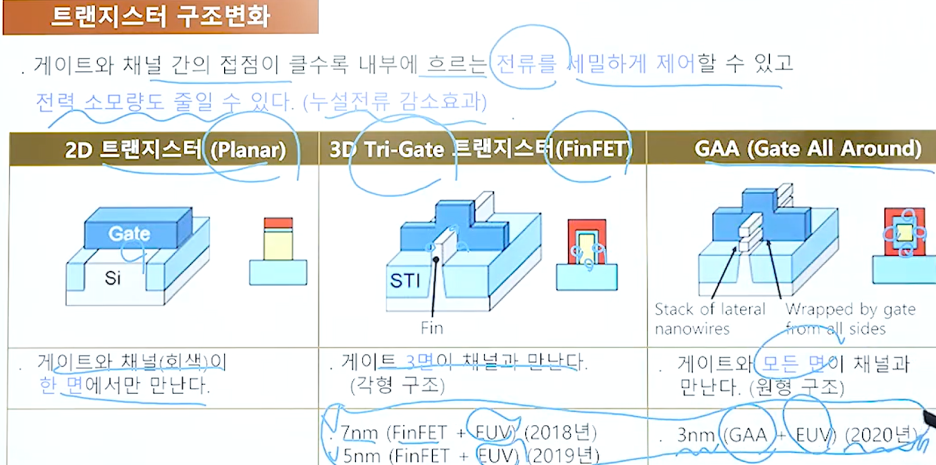

Transistor가 동작하지 않을 때 소스와 드레인 사이에 흐르는 누설 전류가 발생하는데, 트렌지스터의 선폭이 줄어들스록 SCE(Short Channel Effect)가 발생하여 누설전류가 증가하고 이로 인해 소모되는 전력량 증가

> 누설전류 개선을 위해 28nm 공정부터 HKMG(High-k Metal Gate)를 적용

: 누설전류를 줄이기 위해 게이트 절연막 두께를 늘리는 방법으로 가능하나 절연막의 두께도 공정상 한계에 도달하여 유전율이 높은 물질(high-k dielectric)로 대체하면 누설전류를 제어할 수 있다.> 28nm공정부터 게이트 절연막을 SiO2(low-k)에서 HfO2(high-k)로 변경

>14nm공정부터 FinFET공정 적용

14nm 공정부터는 재료를 변경(HKMG)하는 것으로 누설전류를 줄이는데 한계가 발생하여 FinFET공정 적용 : 전자의 흐름을 양쪽 게이트 압력으로 차단하여 누설전류를 최소화 하는 개념

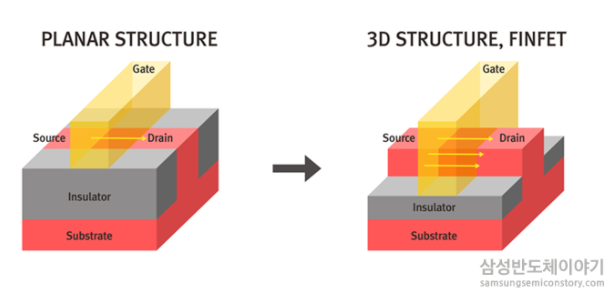

FinFET

:기존 평면 구조의 한계를 극복하기 위해 도입된 입체 구조의 공정기술

트랜지스터는 게이트에 전압이 가해지면 채널을 통해 'Source'에서 'Drain'으로 전류가 흐르며 동작하게 된다. 이때 게이트와 채널과의 접점이 클수록 효율이 높아지는데, 핀펫 공정은 핀(Fin) 모양의 3D 구조를 적용, 접점 면적을 키워 반도체 성능 향상 및 누설 전류를 줄였다.

체널을 돌출시킴으로서 게이트의 길이가 동일한 편면 소자보다 유효부피가 큰 채널을 만들 수 있다.

6) 트렌지스터 구조 변화

2. 파운드리 산업

4차 산업 혁명의 핵심인 IoT, 빅데이터, AI 등의 신기술의 고집적도의 반도체를 요구하기 때문

'공학 > 반도체' 카테고리의 다른 글

| Etching 공정 : 정의, dry etching 종류, 중요 parameter, 필요요소, 플라즈마 (0) | 2023.06.19 |

|---|---|

| 플라즈마 사용 공정 : dry etch (0) | 2023.06.19 |

| 습식 / 건식 식각 공정 (2) | 2023.06.06 |

| 반도체 전공정(웨이퍼 제작, 산화, 포토, 식각, 증착&이온주입, 금속배선, CMP) (4) | 2023.06.06 |

| 웨이퍼 특성 검사(EDS), 패키징, TSV, 패키지 특성 검사, MOSFET구조 및 동작원리, PN접합다이오드, 단 채널 효과 (2) | 2023.06.06 |

댓글